在电子硬件研发领域,有一个让无数项目经理和采购头疼的“潜规则”:打样顺利,不代表量产顺利。

我们经常遇到这样的场景:工程师满怀信心地拿着10片样板进行功能测试,一切指标完美,性能达标。但当订单量扩大到1000片、5000片时,问题开始像“挤牙膏”一样陆续浮现——有的板子电容贴歪了,有的BGA芯片虚焊,甚至同一批次的板子,有些能正常工作,有些却发热严重。

随之而来的是一连串的连锁反应:

- 成本失控: 良率从98%暴跌至70%,废品率飙升,原本核算好的成本瞬间变成亏损;

- 交期延误: 产线频繁停机调整参数,采购被迫加急补料,最终导致产品错过最佳上市窗口;

- 品质投诉: 后端组装厂抱怨板子尺寸不一致,客户投诉产品故障率偏高。

为什么会出现这种“样板跑得通,量产跑不动”的情况?根本原因往往只有一个:设计在原理上没有问题,但并没有考虑制造可行性(DFM)。

什么是DFM?为什么它不仅仅是“生产前检查”

提到DFM,很多人的第一反应是:把Gerber文件发给板厂,让他们检查一下能不能做出来。

这是一个非常普遍的误区。真正的DFM,绝不仅仅是投板前的一次“体检”,而是一套贯穿于产品开发全流程的并行工程思维。

简单来说,DFM就是在设计阶段就提前预判制造、装配和测试过程中可能遇到的工艺难点。它要求设计师跳出“只要原理通,板子就能用”的思维定势,站在生产线的角度去审视每一根走线、每一个过孔和每一颗元器件的摆放。

更准确地说,DFM不是生产的前置环节,而是设计与制造之间的沟通桥梁。这个桥梁搭建得越早,后期“翻车”的概率就越低。

设计阶段:DFM问题最容易被提前解决

有一组数据在行业里流传甚广:设计阶段决定了产品最终80%以上的制造成本和制造难度。 在这个阶段修改一个设计错误,可能只需要几分钟和零成本;但如果等到开模完成或者上了产线才发现问题,付出的代价将是几何级的增长。

在设计阶段,DFM审查的核心应聚焦于以下几个维度:

1. PCB结构设计的合理性

- 层数规划: 层数越多,压合工艺越复杂。是否必须用8层板?6层能否满足信号完整性?

- 板厚与孔径比: 板厚如果超过10mm,而最小孔径只有0.2mm,钻孔时的断刀风险和电镀难度都会急剧上升。

- 叠层对称性: 不对称的叠层结构会导致板材在高温回流焊时发生翘曲,进而引发BGA虚焊。

2. 布局与布线的工艺友好性

- 器件间距: 两颗紧密的阻容件距离太近,贴片机吸嘴在贴装时可能会撞到已贴好的元件。

- 焊盘设计: 焊盘过大或过小,都会影响回流焊时的锡膏流动性。特别是对于Chip元件,不合理的焊盘设计极易导致“立碑”现象。

- 热设计: 大面积的铜箔区域是否加了散热过孔?如果没有,焊接大功率器件时可能会出现“冷焊”。

3. 制造极限的确认

线宽线距是否在工厂的标准工艺能力之内?强行挑战极限精度,意味着良率的大幅妥协。

PCB制造阶段:避免工艺限制导致设计返工

当设计数据进入制造环节,DFM的重心从“设计合理性”转向“工艺匹配性”。PCB制造是一个物理和化学反应的集合,每一个环节都有其物理极限。

在这一阶段,DFM关注的典型痛点包括:

- 板材选择: 如果你的设计要求高TG(玻璃化转变温度)板材,但为了降成本选了普通FR4,过回流焊时板子可能会软化变形。

- 铜厚与蚀刻: 设计要求外层铜厚2oz,但线路间距只有4mil。对于制造商来说,厚铜蚀刻时容易产生“侧蚀”,导致线路实际宽度变细,阻抗失控。

- 钻孔公差: 设计师通常希望过孔越小越好,但微孔的成本是普通通孔的5倍以上。如果非功能孔的孔径过小,钻头易断,拉长生产周期。

很多时候,设计文件之所以被工厂退回要求修改,正是因为设计参数超出了工厂的标准流程能力。这种“来回沟通”不仅浪费了时间,也消耗了彼此的信任。

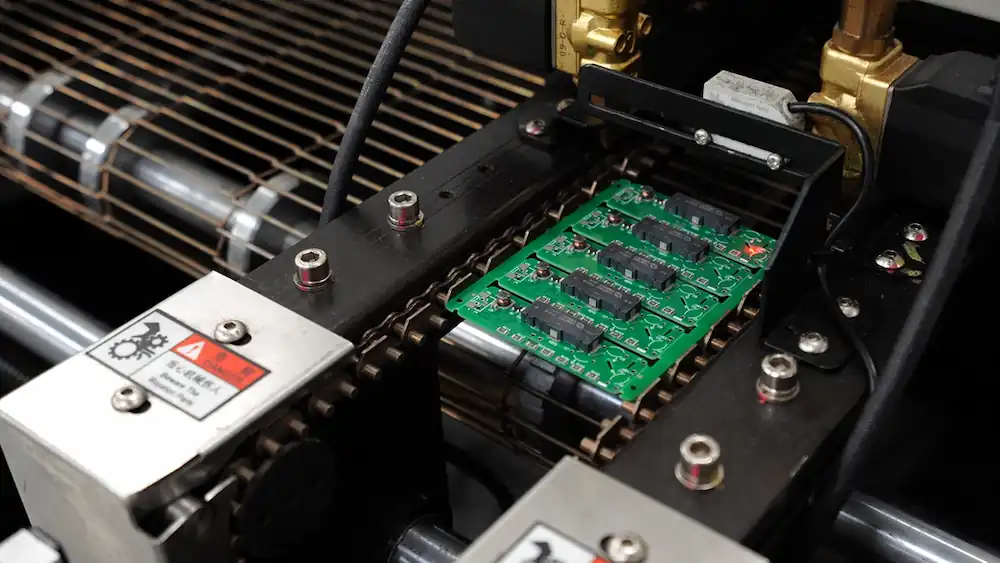

PCBA装配阶段:很多问题在这里才真正暴露

即便PCB裸板制造完美,真正的考验才刚刚开始。SMT贴片和DIP插件环节,是DFM问题的高发地带。

在装配线上,常见的灾难性场景包括:

- 器件干涉: 高器件靠太近回流焊热风回流区,导致阴影效应,一侧锡熔一侧不熔。

- 焊盘与引脚不匹配: 对于BGA或QFN封装,如果焊盘设计没有适当的“扇出”,或者阻焊桥尺寸不对,焊接时极易造成桥接或开路。

- 热分布不均: PCB上如果有大体积的连接器和小阻容件共存,在回流焊炉中,大体积件吸热多,小件升温快,容易导致局部温差过大,出现“立碑”或虚焊。

这些问题的可怕之处在于:它们往往不是100%发生,而是呈现出间歇性缺陷。比如,只有气温低的冬天,或者换了某批次锡膏时,问题才集中爆发,排查起来极其困难。

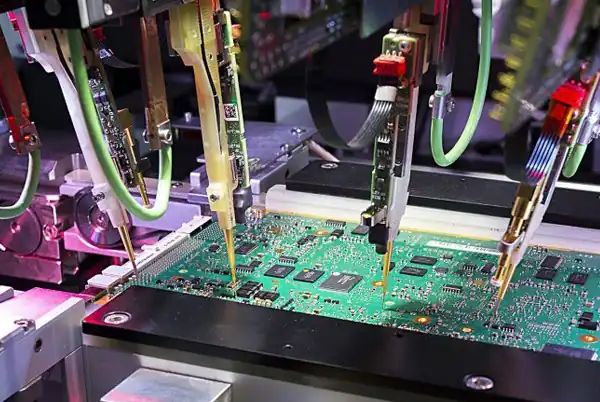

测试与验证阶段:确保量产稳定性

DFM不仅关乎“能不能生产出来”,更关乎“能不能稳定地测出来”。

很多设计在功能验证阶段依靠工程师用飞线、用万用表点测,但到了量产阶段,这种方式是完全行不通的。

量产级的DFM必须考虑:

- 测试点预留: 是否在PCB上预留了足够的测试焊盘?这些焊盘是否均匀分布,且没有被高大元件遮挡?

- ICT/FCT可行性: 治具探针能否稳定接触到测试点?如果测试点放在了器件底部,针床无法触达,自动测试就无从谈起。

- 边界扫描设计: 对于高密度BGA,是否预留了JTAG接口,以便进行边界扫描测试?

如果在设计阶段忽略了测试的可访问性,量产时的质量控制就只能依靠人工目检,效率和可靠性都将大打折扣。

试产与量产阶段:DFM的最终验证场

试产(NPI)是DFM设计的“照妖镜”。在这个阶段,小批量生产会暴露所有模拟环境无法覆盖的真实问题:

- 装配效率: 某个物料的摆放方向需要贴片机额外旋转90度,导致整体效率下降10%。

- 工艺窗口: 回流焊的温度曲线宽容度如何?是必须精确控制在±1℃,还是±5℃都能良好焊接?

- 材料替代性: 当指定型号的物料缺货时,替代料的引脚工艺(如镀锡 vs 镀银)是否与现有的锡膏匹配?

试产阶段的DFM目标非常明确:通过有限的试错,消除量产时的大规模风险,确保生产流程的顺畅性和一致性。

为什么DFM需要设计团队与制造团队协同?

复盘所有量产翻车的项目,我们往往会发现一个共性:问题出在信息断层上。

- 设计团队的KPI是功能实现、性能达标,他们关注的是“能不能跑起来”。

- 制造团队的KPI是良率、效率和成本,他们关注的是“好不好做”。

如果没有DFM流程,这两者就像两条平行线,直到投产后才被迫交集。

DFM的真正价值,就是打破这堵墙。它通过一套共同的语言(线宽、间距、公差、工艺窗口),让设计工程师理解生产线的痛点,也让工艺工程师提前介入产品定义。最好的DFM,是设计师在画第一根线时,脑子里已经有了产线工人操作的画面。

如何通过DFM降低成本和缩短上市时间?

从商业角度看,DFM不是增加流程,而是消除浪费。它带来的实际效益是立竿见影的:

- 减少改版次数: 一次投板成功,意味着节省2周以上的改版时间和数万元的工程费用。

- 提高直通率: 设计时考虑工艺窗口,产线上的调试时间大幅缩短,直通率从85%提升到98%以上。

- 降低BOM成本: 合理的器件选型(如避免使用超高精度的特殊封装),让采购有更多议价空间。

- 缩短TTM(上市时间): 因为少了折腾,产品能更快进入市场,抢占先机。

【案例】从3次改板到一次成功,我们做了什么?

去年,某客户研发一款工业控制主板。第一版设计在功能测试时完全正常,但进入小批量试产时,发现以下问题:

- 板边预留的工艺边太窄,导致分板时应力集中,损坏了近5%的MLCC电容;

- 两个MOS管紧挨着散热器,回流焊时由于热容量差异大,出现大量虚焊。

在第一次改板后,虚焊问题解决了,但ICT测试点被散热器遮挡,导致无法进行自动化测试,必须人工补测,效率极低。

直到第三次改板,我们提前介入,与客户工程师一起使用DFM软件进行全流程仿真。我们调整了测试点位置,优化了散热过孔布局,并重新规划了器件的禁布区。最终,第四次投板一次性通过试产,量产良率稳定在99.5%以上。客户的项目经理感慨:“原来改三次不算多,后来才发现,最贵的是时间成本。”

总结

回到文章开头的问题:为什么很多项目在量产阶段才出问题?

因为优秀的样板可以通过“手调”来掩盖设计缺陷,而成功的量产,却需要设计本身具备强大的“容错性”和“工艺适应性”。

真正能够稳定量产的PCB项目,很少依赖运气。它们往往在设计阶段,就已经把制造的每一个细节考虑在内。DFM不是生产前的一道关卡,而是一套让设计从“实验室的艺术品”进化为“工业化的商品”的开发方法。

对于硬件工程师来说,掌握DFM思维,意味着从“能用”走向“好用”;对于制造企业来说,推行DFM流程,则是从“能生产”走向“高效、高质量生产”的必经之路。

让设计预见制造,这才是从打样到量产的最短路径。