在电子制造行业,我们经常听到硬件工程师或产品经理发出这样的困惑:“样板跑了10套,功能一切完美,怎么到了试产500套的时候就频频冒烟?” 这种“能打样、不能量产”的现象,几乎成了产品从原型走向市场的“鬼门关”。

对于采购PCBA服务的客户来说,这不仅意味着交付延迟,更意味着研发资金的浪费和市场窗口的错失。但很多人不知道的是,这些量产时的“惊天大雷”,其实早在PCBA的方案设计阶段就已经埋下了引信。

为什么很多PCBA项目会出现“能打样、不能量产?

我们先来描绘一个常见的行业“悲剧”流程:

在打样阶段,工程师像艺术家一样精心手工焊接,样板通电一次成功,功能完美,性能达标,客户满意。

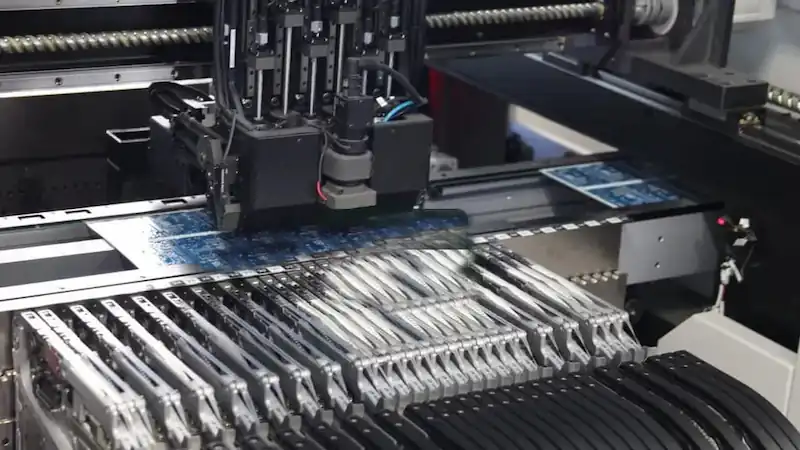

然而,当订单下来进入试产,问题开始像变魔术一样出现:SMT贴片机频繁报警,炉后焊接出现大量虚焊、桥连;好不容易组装的几台,良率却像过山车;采购突然通知某颗核心器件停产或交期长达20周;BOM成本莫名其妙的飙升了30%。

为什么看似一样的图纸,结果却天壤之别?打样验证的是“功能”,而量产考验的是“工业系统”。

打样阶段,你可以用手工焊接弥补封装设计的微小缺陷,可以用昂贵的现货市场物料替代紧缺芯片。但量产阶段,机器不会像人一样“智能”地调整,供应链必须考虑成本和长期稳定。以下三个典型场景,是隐患最常见的藏身之处:

- 手工与机器的鸿沟:打样时工程师用烙铁能轻松搞定0.4mm间距的引脚,但SMT产线上,锡膏印刷稍微偏移一点就会导致大面积桥连。

- 器件供应的断层:打样用的是从某宝买的拆机件或者代理商借的样品,量产时才发现该型号已被原厂标记为“不推荐新设计”。

- 工艺窗口的忽视:PCB设计只考虑了“通电”,没考虑“高温焊接”。焊盘过大导致立碑,散热不均导致冷焊。

设计阶段只考虑“功能实现”,忽略制造可行性

很多研发团队在方案阶段是“功能至上”的。原理图正确、逻辑无误、代码跑通,项目就认为完成了80%。但对于PCBA制造端而言,真正的关注点完全不同:这块板能不能被机器识别?贴片头能不能吸起来?回流焊时能不能自校正?

常见的设计“坑”往往集中在DFM(可制造性设计)领域:

- 过密的器件布局:为了缩小PCB体积,将电容紧贴芯片边缘放置。这在手工焊时没问题,但在高速贴片机贴装时,吸嘴可能会撞到已贴好的邻件,导致抛料或移位。

- 不合理的焊盘设计:例如,对于QFN(方形扁平无引脚封装)芯片,如果内部散热焊盘的锡膏量设计不当,要么导致元件浮高(地脚虚焊),要么导致锡膏挤出短路。

- 测试点的缺失:原理图上功能测试点都有了,但没转成PCB上的实体测试焊盘。导致量产时ICT(在线测试)针床无从下手,只能人工用示波器探头一个个点,效率极低。

DFM的核心逻辑是: 设计人员在画图时,就要想象这块板正在经历SMT产线的贴装、回流和分板过程,确保每个设计都在制造设备的“容忍度”之内。

打样阶段使用的器件,在量产阶段可能无法稳定供应

这是PCBA项目中最具杀伤力的“隐形杀手”。样机阶段的物料策略往往是“不管黑猫白猫,能抓到老鼠就是好猫”。

你可能在打样时用了以下几种“危险”物料:

- 特殊封装的冷门料:为了一个特殊性能,选了一款只有某小厂生产的BGA封装芯片。打样时买了几颗没问题,量产时发现该代理商说“需原厂订货,交期24周”。

- 即将停产的“孤儿料”:使用了某大厂的一款经典MCU,但未核实其生命周期状态。量产时才发现该型号已进入EOL(停产)流程,被迫高价从现货市场扫货。

- 尺寸独特的接插件:为了美观选了一款非主流的Type-C连接器,打样时手工焊接尚可。量产时自动插件机无法适配该来料包装,且该品牌在主流代理商处无备货。

解决方案在于BOM风险评估:

在方案设计阶段,硬件的选型工程师就应该像采购一样思考:

- 是否主流:优先选用封装通用、多家大厂兼容的物料。

- 是否长生命周期:核对原厂发布的生命周期状态,避免选择“NRND”(不推荐用于新设计)的型号。

- 是否有备选方案:关键元器件(如电源IC、MCU)在原理图设计时就预留第二供应商的兼容封装(P2P兼容),做到“一颗芯片,两个来源”。

PCB设计没有考虑量产工艺窗口

PCB打样通常数量少,板厂往往用最稳定的工艺参数、最充足的加工时间来做。但量产时,面对成千上万块板,工艺参数的“窗口”大小决定了良率高低。

常见的量产工艺痛点包括:

- 焊盘设计不合理:

- 立碑现象:对于0402或0201的阻容件,如果其中一个焊盘连接了粗大的地线铜箔,散热过快,导致两端锡膏熔化时间不一致,元件就会像墓碑一样竖起来。

- 引脚间距过小:设计时为了走线方便,将IC引脚间距压缩到了IPC标准的极限以下。导致钢网开窗困难,印刷稍微错位就桥连。

- 走线和布局的热问题:

- 散热不均:大面积的铜箔没有设计“热焊盘”(Thermal Relief),导致焊接时热量被快速导走,形成虚焊(冷焊)。

- 回流阴影:在高器件密度的板子上,将大器件(如变压器)布局在小型贴片电容的紧下风处。回流焊时,大器件阻挡了热风对流,导致小器件焊接不良。

- 工艺复杂度过高:为了省一点空间,设计了6层板甚至HDI板,但实际产品需求4层板完全够用。复杂的PCB工艺不仅增加了成本,也增加了生产周期和报废率。

因此,PCB设计不仅要过得了仿真软件,更要过得了产线工人的经验关。电气性能与制造可行性必须双轨并行。

没有为测试和调试预留设计空间

在打样阶段,工程师往往拥有“上帝视角”。他们可以轻松地用万用表笔点到IC的引脚上,可以飞线连接调试器,甚至可以用热风枪随意拆换元件。

但量产线上,工人不是开发者,测试设备是死的。

如果方案阶段没考虑测试,量产时就会面临:

- ICT无法覆盖:所有关键网络(电源、地、关键信号)都需要预留出测试点。如果测试点被器件压在下面,或者孔径太小无法容纳探针,ICT针床就无法进行自动化开路/短路测试。

- 功能测试效率低下:没有设计统一的FCT(功能测试)接口,每次测试都需要手工连接杜邦线,不仅容易接错,而且效率极低,无法满足产线节拍。

- 故障定位难:没有预留调试用的串口或JTAG接口,一旦产品在老化测试中出问题,维修人员只能破坏性拆解,无法快速读取内部日志。

设计建议:

- 强制预留测试点:将测试点标准化(例如直径1.0mm的裸铜焊盘),并确保所有网络都能通过探针接触。

- 模块化测试接口:设计一个专用的FCT金手指或连接器,将所有测试信号引出,便于开发自动化测试治具。

- 板载调试功能:预留LED指示灯或简单的按键,用于产线快速验证基础功能。

没有考虑真实使用环境带来的可靠性问题

实验室环境通常是恒温恒湿、电源纯净、无振动的“温室”。但产品最终可能被安装在夏日的户外机柜(高温)、冬天的北方基站(低温)、或者电机旁边(强干扰)。

方案阶段忽略环境应力,量产后常见问题:

- 电源余量不足:实验室测试电源纹波合格,但在高温环境下,电源转换效率下降,负载稍微波动就导致电压跌落,系统重启。

- 三防漆覆盖不全:方案设计时没考虑防潮需求,导致某些高压引脚间距过小。在潮湿环境中,即使喷涂了三防漆,也容易发生电化学迁移(漏电),导致设备损坏。

- EMC设计缺失:为了节约成本,省去了共模电感和滤波电容。实验室测试通过,但到了工业现场,电机起停产生的群脉冲干扰直接让单片机死机。

可靠性设计不是玄学,而是通过降额设计(电容耐压留余量、电流留余量)、热设计(关键发热器件布局考虑散热)和防护设计(ESD、浪涌防护器件)在方案阶段就固化下来的。

如何在PCBA方案阶段提高量产成功率

基于以上痛点,要在方案阶段提高量产成功率,可以总结为以下四个关键行动:

1. 提前进行DFM评审

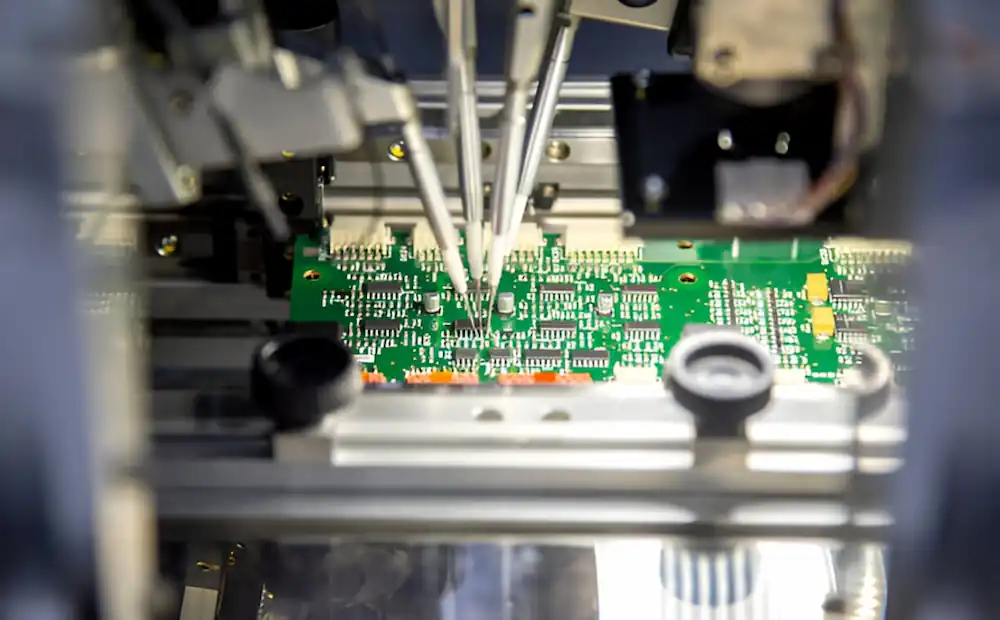

不要等PCB发出去做了再改。在layout完成50%和100%时,邀请PCBA制造商参与评审。利用他们的经验,检查焊盘设计、拼版方式、工艺边添加是否合理。现在的DFM软件可以提前模拟生产,自动检测“孤岛铜皮”、“酸角”等问题。

2. 在方案阶段评估BOM风险

建立BOM的“红黄绿”灯机制:

- 绿灯:主流封装、多品牌通用、生命周期活跃。

- 黄灯:单一直供、交期长、但性能无法替代。

- 红灯:即将停产、难以采购、封装特殊。

方案阶段必须制定红灯物料的替代计划,黄灯物料的安全库存策略。

3. 与PCBA制造商提前沟通

将PCBA制造商从“供应商”转变为“技术伙伴”。在方案早期,他们可以提供的帮助包括:

- 针对当前PCB层数和线宽,提供成本最优建议。

- 针对特殊器件(如BGA、QFN)提供特殊的钢网开口设计建议,提高焊接良率。

- 分享当前市场上通用的、交期好的主流物料清单。

4. 提前规划测试方案

在设计硬件的同时,就要思考“这个产品怎么批量测试”。将测试点、测试接口作为必须交付物写入设计规范。最好能画出量产测试的流程图,确保每一个功能都是可自动化验证的。

结语

“能打样、不能量产”的本质,是“研发思维”与“工业思维”的脱节。很多风险在原理图闭合的那一刻,其实就已经决定了产品的制造命运。

打样的成功只是证明了想法的可行性,而量产的胜利才标志着产品的真正成熟。通过在方案设计阶段引入DFM理念、严控BOM风险、优化PCB工艺、前瞻测试方案,您不仅能避开那些令人头疼的“量产坑”,更能大幅缩短产品上市周期,降低综合制造成本。

下一次,当您的PCBA设计启动时,不妨多问一句:这个设计,准备好上产线了吗?