“张工,我们这版方案明明样机跑得好好的,为什么一到你们工厂评审就被打回来了?是不是配合上有问题?”

这是我们工程部经常听到的客户疑问。很多工程师的第一反应是工厂“找麻烦”或“能力不足”,但真实情况恰恰相反——打回,是工厂对你量产风险的最后预警。

实际上,超过80%的“打回”都发生在DFM(可制造性设计)工程评审阶段。工厂评审的本质不是否定你的设计,而是识别那些在实验室可行、但在流水线上会变成灾难的设计隐患。核心就一句话:被打回 ≠ 方案不能用,而是方案“不适合稳定量产”。

下面,我们以真实评审案例和工厂工程师的口吻,拆解那些最容易导致方案被“毙掉”的设计雷区。

一、 封装与焊接设计:你的板子,我的产线“焊不上”

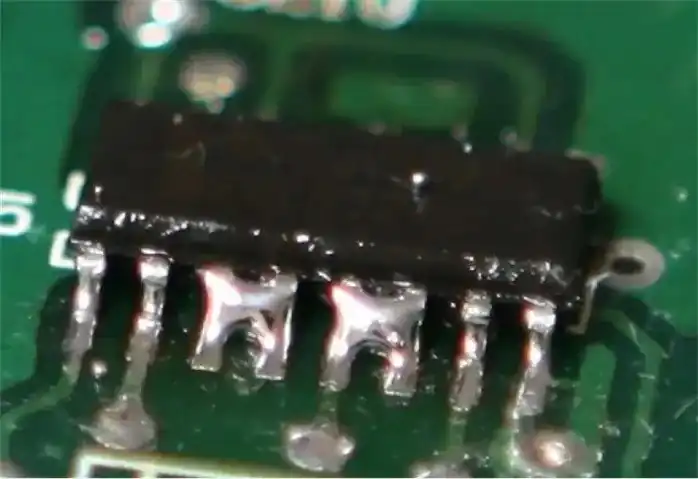

案例1:冷门封装,钢网都没法开

客户方案:为了体积极致化,选用了一颗QFN封装芯片,但引脚间距(pitch)是非标准的0.3mm,且封装尺寸厂家自定。

工厂视角:这种封装不在IPC标准库,我们的通用钢网开口方案完全不适用。需要单独开刻激光钢网,但极窄的间距会导致锡膏释放率不可控。

评审打回意见:“封装Pitch 0.3mm非标,现有产线钢网工艺窗口不足,连锡风险>30%,建议改为标准0.4mm pitch封装或提供专项工艺验证报告。”

案例2:焊盘画“飞了”,IPC标准是摆设?

客户方案:0603电阻焊盘,长度做得偏短,宽度又过大,说是为了“节省空间”。

工厂视角:这直接违反了IPC-7351标准。回流焊时,元件会因为表面张力“立碑”(墓碑效应),或者一端虚焊。这不是调试能解决的,是物理定律。

评审打回意见:“0603封装焊盘设计不符合IPC-A-610 Class 2标准,L尺寸不足,实测立碑风险极高。请按IPC标准库更新封装,否则量产良率无法保证。”

二、 元器件采购:你今天能买到,明天还能吗?

案例3:芯片已“濒危”,你却当主流

客户方案:BOM里一颗核心电源芯片,客户自己在某样品网站买到了10片,型号在原厂官网已标注为“NRND”(不建议用于新设计)。

工厂视角:这是颗“死料”!现在小批量可能还能凑齐,一旦量产上千套,要么断货,要么只能从市场翻新料里挑,质量风险工厂背不起。

评审打回意见:“U5芯片型号已处于NRND状态,原厂交期无法承诺,存在断供风险。请提供至少一个pin-to-pin兼容的替代型号,否则不予接单。”

案例4:BOM是“独苗”,断了就全军覆没

客户方案:所有关键器件都只列了一个厂家、一个型号,且声称“别无替代”。

工厂视角:供应链只要波动一次(比如疫情、火灾、贸易制裁),你的项目就得停产。工厂最怕这种“把鸡蛋放在一个篮子里”的BOM,风险完全不可控。

评审打回意见:“BOM单一来源比例超过70%,尤其核心器件无第二货源。请务必提供关键器件的替代料方案,否则需签署《物料断供风险自担承诺书》。”

三、 PCB结构与拼板:板子自己就“拧巴”,怎么上流水线?

案例5:板子太薄,过炉像“面条”

客户方案:为了柔性穿戴设备,采用0.6mm超薄板,且未设计任何工艺边或支撑治具。

工厂视角:这么薄的板子,在回流焊高温下会严重翘曲。过SMT贴片机时,传送轨道都可能卡住,更别提焊接精度了。

评审打回意见:“板厚0.6mm,无工艺边,SMT传送及回流焊翘曲风险极高。建议增加至1.0mm,或至少增加5mm工艺边并设计专用载具(治具费另计)。”

案例6:拼板设计“反人类”,得分板还得上手术刀

客户方案:为了省板费,采用复杂的异形拼板,V-CUT线画在了贴片元件下方。

工厂视角:分板时应力会直接传递到元件焊点,导致隐性裂纹。我们的自动分板机也无从下刀。

评审打回意见:“V-CUT位置穿越0402电阻下方,分板应力将导致焊点可靠性失效。请重新设计拼板方式,V-CUT必须远离元件体至少2mm。”

四、 测试方案:你让我怎么测?用意念吗?

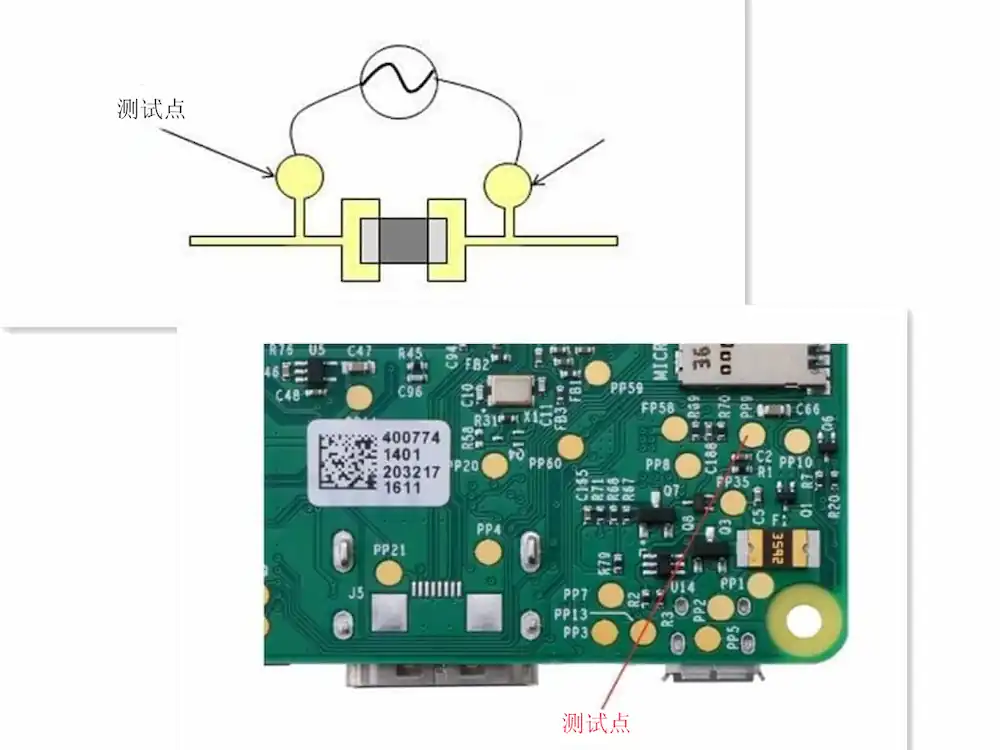

案例7:测试点?不存在的

客户方案:板上密密麻麻,所有信号点都被芯片和器件盖住,完全没有预留测试点。

工厂视角:没有测试点,意味着我们无法进行ICT(在线测试)和FCT(功能测试)。只能靠“通电看冒不冒烟”来检验,这种板子流入市场,客诉率会爆表。

评审打回意见:“所有关键电源、信号网络均未引出测试点,无法实施量产测试。请至少对电源、地、主要数字总线(如I2C、SPI)预留1mm直径的测试孔或测试点。”

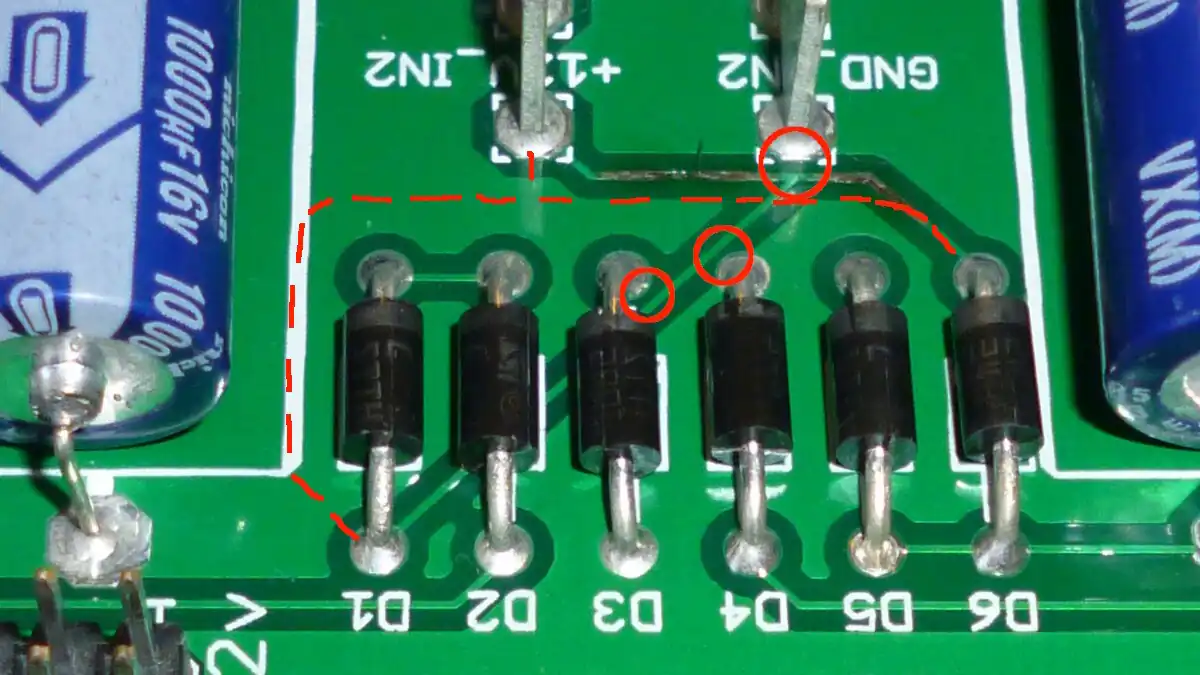

案例8:测试点藏在了“盘丝洞”

客户方案:勉强放了几个测试点,但全挤在贴片元件中间,间距不到0.5mm。

工厂视角:测试探针直径是0.8mm。你这点距,我们的针床做不了,飞针测试效率极低还容易短路。

评审打回意见:“测试点间距0.5mm,低于标准针床探针中心距1.27mm要求。请将测试点间距调整至≥1.27mm,并布局在元件稀疏区域。”

五、 对工艺能力的“幻想”:实验室 ≠ 流水线

案例9:你以为我们厂是“复仇者联盟”基地?

客户方案:直接扔过来一个10层任意阶HDI板设计,要求做0.2mm的BGA。

工厂视角:我们有能力清单的!不是所有工厂都能做高级HDI和超细间距BGA。这种设计需要专项评估设备和工艺,成本和时间都不是常规项目能承担的。

评审打回意见:“0.2mm BGA及10层任意阶HDI超出我司标准工艺能力。如确需生产,需启动特殊工艺评审,报价及周期将大幅增加。”

案例10:设计在“走钢丝”,良率靠玄学

客户方案:阻抗线要求控制±5%,但走线在电源分割层来回跨缝。

工厂视角:理论计算可行,但PCB加工存在公差,层压对位也有偏差。这种设计会让阻抗实际值离散极大,工厂做不到全程100%符合。

评审打回意见:“此阻抗设计对加工公差过于敏感,预估量产良率低于85%。建议放宽控制要求至±10%,或优化叠层与走线设计。”

六、 资料交付:“谜语人”式文件,全靠猜?

案例11:“三件套”对不上,上演罗生门

客户方案:Gerber文件是V2.1,BOM是V2.0,坐标文件又是V1.9。而且BOM里有个料号,在PCB上根本找不到位置。

工厂视角:我们该以哪个为准?一旦做错,损失谁承担?这种基本错误,说明内部流程混乱,我们不敢接。

评审打回意见:“Gerber、BOM、坐标文件版本不一致,且BOM中C15在PCB上无对应位号。请提供完整且版本统一的生产资料包,否则评审中止。”

为什么这些问题总在最后才发现?

因为开发流程错位了。方案阶段只管功能,样机阶段只求点亮,到了要量产时,才把工厂当“魔术师”,希望我们把所有问题“变没”。但工厂的魔法,叫做“标准”和“规范”。

如何避免?给你的核心建议就两条:

- 把DFM评审从“事后关卡”变成“事前工具”:在画原理图、选型、布局时,就同步思考“我的代工厂能不能稳定地把它做出来?”。

- 早期邀请工厂介入:在关键设计节点,把初步方案发给工厂的工程团队做一次预审。花几个小时沟通,可能省掉后面几周的改版和打样。

结语:被“打回”是成本最低的“良药”

说句实在话,我们工厂最怕的不是“打回”你的方案,而是硬着头皮生产,然后在量产中批量出事。那时面临的将是停线、报废、赔款和信誉损失。

被打回,是工厂在替你踩刹车,是在为你的项目扫雷。真正危险的,从来不是被打回的设计,而是那些本应被打回、却侥幸流入生产线的设计。

如果你的方案希望一次通过评审,顺利走向量产,能波达可以提供:

- PCBA方案可制造性(DFM)预评审服务:在投板前,由资深工程师为你把关设计。

- 元器件可采购性与替代料分析:提前规避断供风险,优化BOM成本。

- 从设计到量产的一站式协同:让制造思维前置,让你的创意高效、可靠地变成产品。